This is a Read-The-Fine-Manual moment. See the <value> argument description under the force command Arguments section in the Command Reference Manual.

A one-dimensional array of character enumeration can be forced as a sequence of character literals or as a based number with a radix of 2, 8, 10 or 16. For example, the following values are equivalent for a signal of type bit_vector (0 to 3):

You could note that IEEE Std 1076-2008 15.5.3 Based literals tells us:

A based literal is an abstract literal expressed in a form that specifies the base explicitly. The base shall be at least two and at most sixteen.

There are VHDL standard compliant based literals that can't be expressed with the force command.

Also notice the question's use of

force SW 01000001

is compatible with the sequence of character literals example in the Command Reference Manual. See the following NOTE:

For based numbers in VHDL, ModelSim translates each 1 or 0 to the appropriate value for the number’s enumerated type. The translation is controlled by the translation table in the pref.tcl file. If ModelSim cannot find a translation for 0 or 1, it uses the left bound of the signal type (type’left) for that value.

Also note from the question's value and waveform that the right most position of SWs enumeration translates properly. This suggests that the behavior doesn't match the force command <value> description.

In VHDL terms you're being force to use a bit string literal as demonstrated in scary_jeff's answer and not a string literal for providing the value. (Both sans quotation marks).

The character literal sequence is correct according to the example but does not translate correctly. You could wonder if quotation marks would help - how would otherwise force a string type object's value containing a leading space?

As an early MTI Modelsim user the simulator originally only supported VHDL. The problem is either the simulator or the example.

And of course there's the use of a VHDL test bench instead of embedding simulation sequence in a do file.

This method would be portable between VHDL simulators:

entity schal_tb is

end entity;

architecture foo of schal_tb is

signal SW: bit_vector(7 downto 0);

signal LED: bit_vector(7 downto 0);

begin

DUT:

entity work.schal

port map (

SW => SW,

LED => LED

);

STIMULUS:

process

begin

SW <= "01000001";

wait for 20 ns;

SW <= "01000000";

wait for 20 ns;

wait for 60 ns; -- to show 100 ns on waveform

wait; -- suspends process permenently

end process;

end architecture;

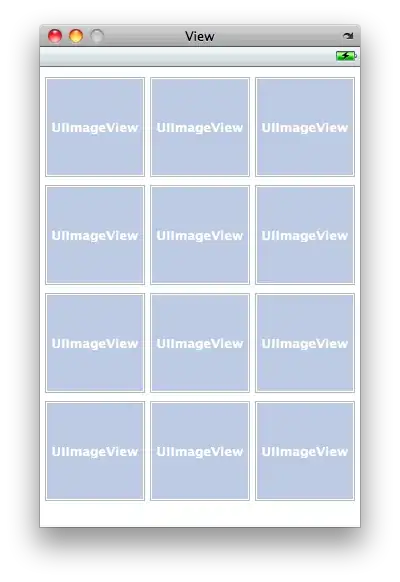

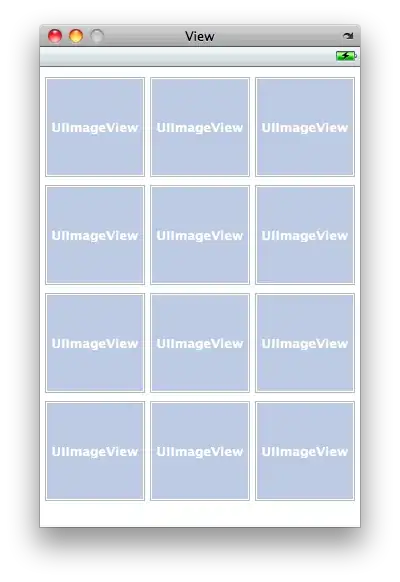

And gives:

There are also online VHDL Testbench outline generators such as the Doulos VHDL Testbench generator or this Online VHDL Testbench Template Generator.