Just pass your tcl file as a parametet to your compiled/fused testbench via -tclbatch <filename>.

.\fifo_tb.exe -tclbatch fifo_tb.tcl -gui

-gui opens the testbench in GUI mode with iSim connected to the testbench executable.

To see all supported options of a testbench, run the testbench executable with -h.

To show all supported TCL commands in iSim, use the help command. I'm currently not aware of any loadfile/source/do instruction for iSim.

Example fifo_cc_got_tb:

All needed VHDL files are listed in a fifo_cc_got_tb.prj file:

vhdl poc "D:\git\PoC\tb\common\my_config_ML505.vhdl"

vhdl poc "D:\git\PoC\tb\common\my_project.vhdl"

vhdl unisim "C:\Xilinx\14.7\ISE_DS\ISE\vhdl\src\unisims\primitive\MUXCY.vhd"

vhdl unisim "C:\Xilinx\14.7\ISE_DS\ISE\vhdl\src\unisims\primitive\XORCY.vhd"

vhdl poc "D:\git\PoC\src\common\utils.vhdl"

vhdl poc "D:\git\PoC\src\common\strings.vhdl"

vhdl poc "D:\git\PoC\src\common\vectors.vhdl"

vhdl poc "D:\git\PoC\src\common\board.vhdl"

vhdl poc "D:\git\PoC\src\common\config.vhdl"

vhdl poc "D:\git\PoC\src\common\physical.vhdl"

vhdl poc "D:\git\PoC\tb\common\simulation.v93.vhdl"

vhdl poc "D:\git\PoC\tb\common\simulation.v93.vhdl"

vhdl poc "D:\git\PoC\src\mem\ocram\ocram.pkg.vhdl"

vhdl poc "D:\git\PoC\src\mem\ocram\ocram_sdp.vhdl"

vhdl poc "D:\git\PoC\src\fifo\fifo_cc_got.vhdl"

vhdl test "D:\git\PoC\tb\fifo\fifo_cc_got_tb.vhdl"

The ISE ProjectNavigator collects this information for you and saves it in a prj file.

fuse.exe is executed to compile the testbench from given prj file:

cd D:\git\PoC\temp\isim\

C:\Xilinx\14.7\ISE_DS\ISE\bin\nt64\fuse.exe test.fifo_cc_got_tb --prj fifo_cc_got_tb.prj -o fifo_cc_got_tb.exe

This can also be found in the ProjectNavigator console window:

Started : "Simulate Behavioral Model".

Determining files marked for global include in the design...

Running fuse...

Command Line: fuse -intstyle ise -incremental -lib secureip -o D:/git/GitHub/PicoBlaze-Examples/Projects/SoFPGA_Atlys_ISE/ise/sync_Strobe_isim_beh.exe -prj D:/git/GitHub/PicoBlaze-Examples/Projects/SoFPGA_Atlys_ISE/ise/sync_Strobe_beh.prj PoC.sync_Strobe {}

Running: C:\Xilinx\14.7\ISE_DS\ISE\bin\nt64\unwrapped\fuse.exe -intstyle ise -incremental -lib secureip -o D:/git/GitHub/PicoBlaze-Examples/Projects/SoFPGA_Atlys_ISE/ise/sync_Strobe_isim_beh.exe -prj D:/git/GitHub/PicoBlaze-Examples/Projects/SoFPGA_Atlys_ISE/ise/sync_Strobe_beh.prj PoC.sync_Strobe

The simulation is launched with a TCL script

.\fifo_cc_got_tb.exe -tclbatch ..\..\sim\iSim.gui.tcl -gui

Also this can be seen in the ProjectNavigators console window:

....

Compiled 21 VHDL Units

Built simulation executable D:/git/GitHub/PicoBlaze-Examples/Projects/SoFPGA_Atlys_ISE/ise/sync_Strobe_isim_beh.exe

Fuse Memory Usage: 50240 KB

Fuse CPU Usage: 529 ms

Launching ISim simulation engine GUI...

"D:/git/GitHub/PicoBlaze-Examples/Projects/SoFPGA_Atlys_ISE/ise/sync_Strobe_isim_beh.exe" -intstyle ise -gui -tclbatch isim.cmd -wdb "D:/git/GitHub/PicoBlaze-Examples/Projects/SoFPGA_Atlys_ISE/ise/sync_Strobe_isim_beh.wdb"

ISim simulation engine GUI launched successfully

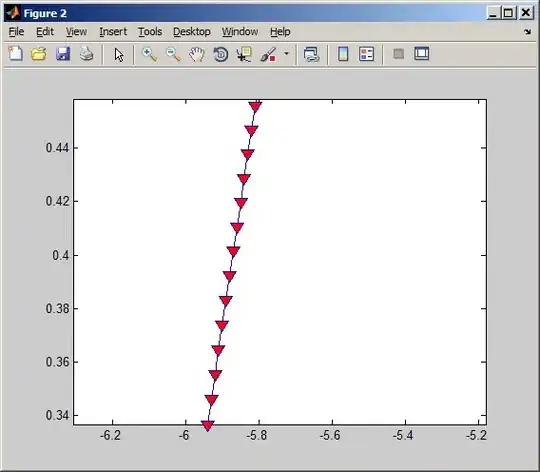

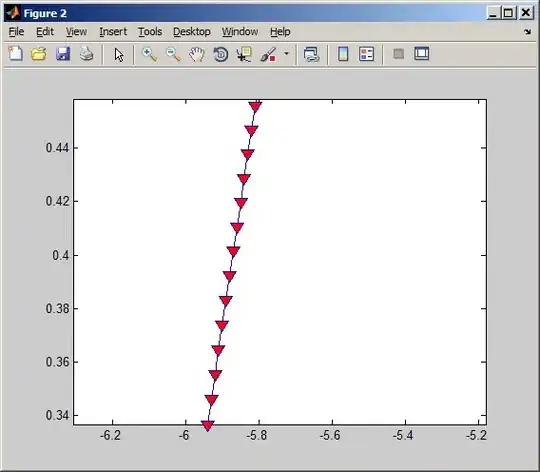

Here is the Simulation Process Property dialog to setup a user defined TCL script (red option) and if needed a user defined waveform configuration file (*.wcfg) green option.