After I finished my design compilation on Quartus, I get multiple result for fmax as shown below. I want to know, what does it means? and How can I calculate the fmax of the all design?.

My design is implementation for the following equation:

for(i = 1; i < 5; i++)

{

T += ( ((Rv[i] - Ru[i]))^2 + ((Iv[i] - Iu[i]))^2 )

}

assume the following: 1. use 4 add-sub, 2 squarer, and eight 21-bit register file(parallel input/output) . 2. finished all operation in 8 clock cycles.

Note: - each adder/subtractor is 21-bit and has a selector pin '1' for add or '0' for sub.

- squarer is 9 bit.

- T is 21 bit.

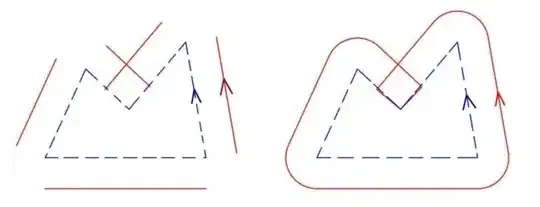

This is the FSM for my design

According the above, this is my code

library ieee;

use ieee.std_logic_1164.all;

use ieee.numeric_std.all;

entity EDCfunction_TopEntity is

port

(

clk, reset : in std_logic;

Rv1 : in std_logic_vector (8-1 downto 0);

Iv1 : in std_logic_vector (8-1 downto 0);

Ru1 : in std_logic_vector (8-1 downto 0);

Iu1 : in std_logic_vector (8-1 downto 0);

Rv2 : in std_logic_vector (8-1 downto 0);

Iv2 : in std_logic_vector (8-1 downto 0);

Ru2 : in std_logic_vector (8-1 downto 0);

Iu2 : in std_logic_vector (8-1 downto 0);

Rv3 : in std_logic_vector (8-1 downto 0);

Iv3 : in std_logic_vector (8-1 downto 0);

Ru3 : in std_logic_vector (8-1 downto 0);

Iu3 : in std_logic_vector (8-1 downto 0);

Rv4 : in std_logic_vector (8-1 downto 0);

Iv4 : in std_logic_vector (8-1 downto 0);

Ru4 : in std_logic_vector (8-1 downto 0);

Iu4 : in std_logic_vector (8-1 downto 0);

T : out std_logic_vector (21-1 downto 0)

);

end EDCfunction_TopEntity;

architecture behavioral of EDCfunction_TopEntity is

type clock_state is (zero, zero_clk2, one, two, two_clk2, three, three_clk2, four, four_clk2, five, six, seven, eight);

type add_sub_type is array (4-1 downto 0) of std_logic_vector (21-1 downto 0);

type squarer_in_type is array (2-1 downto 0) of std_logic_vector (9-1 downto 0);

type squarer_out_type is array (2-1 downto 0) of std_logic_vector (18-1 downto 0);

signal cc_state, cn_state : clock_state;

signal clk_reg_file, reset_reg_file, s_wr_en : std_logic;

signal add_sub_flage, state_mux : std_logic_vector (4-1 downto 0);

signal dataa_add_sub, datab_add_sub, result_add_sub : add_sub_type;

signal dataa_squarer : squarer_in_type;

signal result_squarer : squarer_out_type;

signal w_addr_reg_file, r_addr_reg_file : std_logic_vector (8-1 downto 0);

signal s_w_data_0, s_w_data_1, s_w_data_2, s_w_data_3, s_w_data_4, s_w_data_5, s_w_data_6, s_w_data_7,

s_r_data_0, s_r_data_1, s_r_data_2, s_r_data_3, s_r_data_4, s_r_data_5, s_r_data_6, s_r_data_7

: std_logic_vector (21-1 downto 0);

alias R0 is s_w_data_0(21-1 downto 0);

alias R0H is s_w_data_0(21-1 downto 10);

alias R0L is s_w_data_0(9 downto 0);

alias R1 is s_w_data_1(21-1 downto 0);

alias R1H is s_w_data_1(21-1 downto 10);

alias R1L is s_w_data_1(9 downto 0);

alias R2 is s_w_data_2(21-1 downto 0);

alias R2H is s_w_data_2(21-1 downto 10);

alias R2L is s_w_data_2(9 downto 0);

alias R3 is s_w_data_3(21-1 downto 0);

alias R3H is s_w_data_3(21-1 downto 10);

alias R3L is s_w_data_3(9 downto 0);

alias R4 is s_w_data_4(21-1 downto 0);

alias R4H is s_w_data_4(21-1 downto 10);

alias R4L is s_w_data_4(9 downto 0);

alias R5 is s_w_data_5(21-1 downto 0);

alias R5H is s_w_data_5(21-1 downto 10);

alias R5L is s_w_data_5(9 downto 0);

alias R6 is s_w_data_6(21-1 downto 0);

alias R6H is s_w_data_6(21-1 downto 10);

alias R6L is s_w_data_6(9 downto 0);

alias R7 is s_w_data_7(21-1 downto 0);

alias R7H is s_w_data_7(21-1 downto 10);

alias R7L is s_w_data_7(9 downto 0);

component lpm_adder_subtractor

port

(

add_sub : IN STD_LOGIC ;

dataa : IN STD_LOGIC_VECTOR (20 DOWNTO 0);

datab : IN STD_LOGIC_VECTOR (20 DOWNTO 0);

result : OUT STD_LOGIC_VECTOR (20 DOWNTO 0)

);

end component;

component lpm_squarer

PORT

(

dataa : IN STD_LOGIC_VECTOR (8 DOWNTO 0);

result : OUT STD_LOGIC_VECTOR (17 DOWNTO 0)

);

end component;

component register_file

port

(

clk, reset : in std_logic;

wr_en : in std_logic;

w_addr : in std_logic_vector (8-1 downto 0);

w_data_0 : in std_logic_vector (21-1 downto 0);

w_data_1 : in std_logic_vector (21-1 downto 0);

w_data_2 : in std_logic_vector (21-1 downto 0);

w_data_3 : in std_logic_vector (21-1 downto 0);

w_data_4 : in std_logic_vector (21-1 downto 0);

w_data_5 : in std_logic_vector (21-1 downto 0);

w_data_6 : in std_logic_vector (21-1 downto 0);

w_data_7 : in std_logic_vector (21-1 downto 0);

r_addr : in std_logic_vector (8-1 downto 0);

r_data_0 : out std_logic_vector (21-1 downto 0);

r_data_1 : out std_logic_vector (21-1 downto 0);

r_data_2 : out std_logic_vector (21-1 downto 0);

r_data_3 : out std_logic_vector (21-1 downto 0);

r_data_4 : out std_logic_vector (21-1 downto 0);

r_data_5 : out std_logic_vector (21-1 downto 0);

r_data_6 : out std_logic_vector (21-1 downto 0);

r_data_7 : out std_logic_vector (21-1 downto 0)

);

end component;

begin

A0 : lpm_adder_subtractor port map (add_sub_flage(0), dataa_add_sub(0), datab_add_sub(0), result_add_sub(0));

A1 : lpm_adder_subtractor port map (add_sub_flage(1), dataa_add_sub(1), datab_add_sub(1), result_add_sub(1));

A2 : lpm_adder_subtractor port map (add_sub_flage(2), dataa_add_sub(2), datab_add_sub(2), result_add_sub(2));

A3 : lpm_adder_subtractor port map (add_sub_flage(3), dataa_add_sub(3), datab_add_sub(3), result_add_sub(3));

S0 : lpm_squarer port map (dataa_squarer(0), result_squarer(0));

S1 : lpm_squarer port map (dataa_squarer(1), result_squarer(1));

U0 : register_file port map (clk, reset_reg_file, s_wr_en, w_addr_reg_file, s_w_data_0, s_w_data_1, s_w_data_2,

s_w_data_3, s_w_data_4, s_w_data_5, s_w_data_6, s_w_data_7, r_addr_reg_file,

s_r_data_0, s_r_data_1, s_r_data_2, s_r_data_3, s_r_data_4, s_r_data_5, s_r_data_6,

s_r_data_7);

process (cc_state, reset, Rv1, Iv1, Ru1, Iu1, Rv2, Iv2, Ru2, Iu2, Rv3, Iv3, Ru3, Iu3, Rv4, Iv4, Ru4, Iu4)

begin

case cc_state is

when zero =>

s_wr_en <= '1';

w_addr_reg_file <= "11111111";

R0H <= std_logic_vector(resize(signed(Rv1), R0H'length));

R0L <= std_logic_vector(resize(signed(Ru1), R0L'length));

R1H <= std_logic_vector(resize(signed(Iv1), R1H'length));

R1L <= std_logic_vector(resize(signed(Iu1), R1L'length));

R2H <= std_logic_vector(resize(signed(Rv2), R2H'length));

R2L <= std_logic_vector(resize(signed(Ru2), R2L'length));

R3H <= std_logic_vector(resize(signed(Iv2), R3H'length));

R3L <= std_logic_vector(resize(signed(Iu2), R3L'length));

R4H <= std_logic_vector(resize(signed(Rv3), R4H'length));

R4L <= std_logic_vector(resize(signed(Ru3), R4L'length));

R5H <= std_logic_vector(resize(signed(Iv3), R5H'length));

R5L <= std_logic_vector(resize(signed(Iu3), R5L'length));

R6H <= std_logic_vector(resize(signed(Rv4), R6H'length));

R6L <= std_logic_vector(resize(signed(Ru4), R6L'length));

R7H <= std_logic_vector(resize(signed(Iv4), R7H'length));

R7L <= std_logic_vector(resize(signed(Iu4), R7L'length));

--clk_reg_file <= '1';

--T <= result_add_sub(0);

cn_state <= zero_clk2;

when zero_clk2 =>

r_addr_reg_file <= "11111111";

cn_state <= one;

when one =>

s_wr_en <= '0';

--w_addr_reg_file <= "00001111";

add_sub_flage(0) <= '0';

add_sub_flage(1) <= '0';

add_sub_flage(2) <= '0';

add_sub_flage(3) <= '0';

--r_addr_reg_file <= "00001111";

dataa_add_sub(0) <= std_logic_vector(resize(signed(s_r_data_0 (21-1 downto 10)), dataa_add_sub(0)'length));

datab_add_sub(0) <= std_logic_vector(resize(signed(s_r_data_0 (9 downto 0)), dataa_add_sub(0)'length));

--s_w_data_0 <= result_add_sub(0);

--w_addr_reg_file <= "00000001";

dataa_add_sub(1) <= std_logic_vector(resize(signed(s_r_data_1 (21-1 downto 10)), dataa_add_sub(1)'length));

datab_add_sub(1) <= std_logic_vector(resize(signed(s_r_data_1 (9 downto 0)), dataa_add_sub(1)'length));

--s_w_data_1 <= result_add_sub(1);

--w_addr_reg_file <= "00000010";

dataa_add_sub(2) <= std_logic_vector(resize(signed(s_r_data_2 (21-1 downto 10)), dataa_add_sub(2)'length));

datab_add_sub(2) <= std_logic_vector(resize(signed(s_r_data_2 (9 downto 0)), dataa_add_sub(2)'length));

--s_w_data_2 <= result_add_sub(2);

--w_addr_reg_file <= "00000100";

dataa_add_sub(3) <= std_logic_vector(resize(signed(s_r_data_3 (21-1 downto 10)), dataa_add_sub(3)'length));

datab_add_sub(3) <= std_logic_vector(resize(signed(s_r_data_3 (9 downto 0)), dataa_add_sub(3)'length));

--s_w_data_3 <= result_add_sub(3);

--w_addr_reg_file <= "00001000";

--T <= result_add_sub(3);

--clk_reg_file <= '1';

--r_addr_reg_file <= "11110000";

cn_state <= two;

--state_mux <= "0001";

when two =>

s_wr_en <= '1';

w_addr_reg_file <= "00001111";

R0 <= result_add_sub(0);

R1 <= result_add_sub(1);

R2 <= result_add_sub(2);

R3 <= result_add_sub(3);

dataa_squarer(0) <= result_add_sub(0) (9-1 downto 0);

dataa_squarer(1) <= result_add_sub(1) (9-1 downto 0);

dataa_add_sub(0) <= std_logic_vector(resize(signed(s_r_data_4 (21-1 downto 10)), dataa_add_sub(0)'length));

datab_add_sub(0) <= std_logic_vector(resize(signed(s_r_data_4 (9 downto 0)), dataa_add_sub(0)'length));

dataa_add_sub(1) <= std_logic_vector(resize(signed(s_r_data_5 (21-1 downto 10)), dataa_add_sub(1)'length));

datab_add_sub(1) <= std_logic_vector(resize(signed(s_r_data_5 (9 downto 0)), dataa_add_sub(1)'length));

dataa_add_sub(2) <= std_logic_vector(resize(signed(s_r_data_6 (21-1 downto 10)), dataa_add_sub(2)'length));

datab_add_sub(2) <= std_logic_vector(resize(signed(s_r_data_6 (9 downto 0)), dataa_add_sub(2)'length));

dataa_add_sub(3) <= std_logic_vector(resize(signed(s_r_data_7 (21-1 downto 10)), dataa_add_sub(3)'length));

datab_add_sub(3) <= std_logic_vector(resize(signed(s_r_data_7 (9 downto 0)), dataa_add_sub(3)'length));

cn_state <= two_clk2;

when two_clk2 =>

cn_state <= three;

when three =>

--s_wr_en <= '1';

w_addr_reg_file <= "11110011";

R0 <= std_logic_vector(resize(signed(result_squarer(0)), R0'length));

R1 <= std_logic_vector(resize(signed(result_squarer(1)), R0'length));

R4 <= result_add_sub(0);

R5 <= result_add_sub(1);

R6 <= result_add_sub(2);

R7 <= result_add_sub(3);

add_sub_flage(0) <= '1';

dataa_add_sub(0) <= std_logic_vector(resize(signed(result_squarer(0)), dataa_add_sub(0)'length));

datab_add_sub(0) <= std_logic_vector(resize(signed(result_squarer(1)), datab_add_sub(0)'length));

dataa_squarer(0) <= s_r_data_2 (9-1 downto 0);

dataa_squarer(1) <= s_r_data_3 (9-1 downto 0);

cn_state <= three_clk2;

when three_clk2 =>

cn_state <= four;

when four =>

w_addr_reg_file <= "00000110";

R0 <= result_add_sub(0);

R1 <= std_logic_vector(resize(signed(result_squarer(0)), R0'length));

R2 <= std_logic_vector(resize(signed(result_squarer(1)), R0'length));

add_sub_flage(1) <= '1';

dataa_add_sub(1) <= std_logic_vector(resize(signed(result_squarer(0)), dataa_add_sub(1)'length));

datab_add_sub(1) <= std_logic_vector(resize(signed(result_squarer(1)), datab_add_sub(1)'length));

dataa_squarer(0) <= s_r_data_4 (9-1 downto 0);

dataa_squarer(1) <= s_r_data_5 (9-1 downto 0);

cn_state <= four_clk2;

when four_clk2 =>

cn_state <= five;

when five =>

w_addr_reg_file <= "00001110";

R1 <= result_add_sub(1);

R2 <= std_logic_vector(resize(signed(result_squarer(0)), R2'length));

R3 <= std_logic_vector(resize(signed(result_squarer(1)), R3'length));

add_sub_flage(2) <= '1';

dataa_add_sub(0) <= R0;

datab_add_sub(0) <= result_add_sub(1);

dataa_add_sub(2) <= std_logic_vector(resize(signed(result_squarer(0)), dataa_add_sub(2)'length));

datab_add_sub(2) <= std_logic_vector(resize(signed(result_squarer(1)), datab_add_sub(2)'length));

dataa_squarer(0) <= s_r_data_6 (9-1 downto 0);

dataa_squarer(1) <= s_r_data_7 (9-1 downto 0);

cn_state <= six;

when six =>

w_addr_reg_file <= "00001111";

R0 <= result_add_sub(0);

R1 <= result_add_sub(2);

R2 <= std_logic_vector(resize(signed(result_squarer(0)), R2'length));

R3 <= std_logic_vector(resize(signed(result_squarer(1)), R3'length));

add_sub_flage(3) <= '1';

dataa_add_sub(0) <= result_add_sub(0);

datab_add_sub(0) <= result_add_sub(2);

dataa_add_sub(3) <= std_logic_vector(resize(signed(result_squarer(0)), dataa_add_sub(2)'length));

datab_add_sub(3) <= std_logic_vector(resize(signed(result_squarer(1)), datab_add_sub(2)'length));

cn_state <= seven;

when seven =>

w_addr_reg_file <= "00000011";

R0 <= result_add_sub(0);

R1 <= result_add_sub(3);

dataa_add_sub(0) <= result_add_sub(0);

datab_add_sub(0) <= result_add_sub(3);

--R0 <= result_add_sub(0);

--T <= result_add_sub(0);

cn_state <= eight;

when eight =>

w_addr_reg_file <= "00000001";

R0 <= result_add_sub(0);

T <= result_add_sub(0);

cn_state <= zero;

end case;

--if(state_mux = "0001") then

--end if;

end process;

process (clk, reset)

begin

reset_reg_file <= reset;

if(reset = '1') then

cc_state <= zero;

elsif (clk'event and clk = '1') then

cc_state <= cn_state;

end if;

end process;

end behavioral;

Any help, Regards