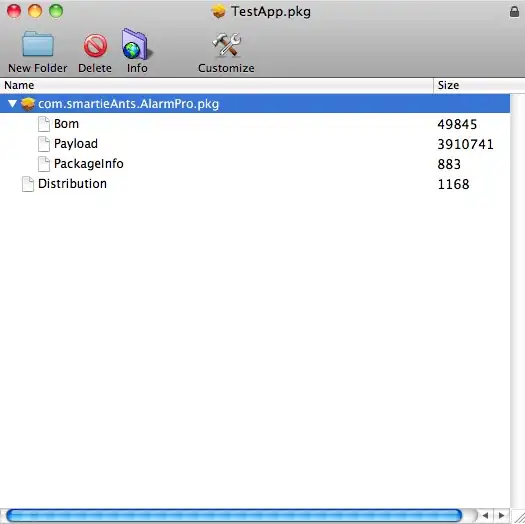

We're doing some work on a CPU in logism in class. We're going over the ALU, and need now need to know different ways multiplication can take place. Our professor gave us two examples, one called the "Five Add Time" and the "31 Add Time" (although I do not believe these are the official names of the algorithm), shown here:

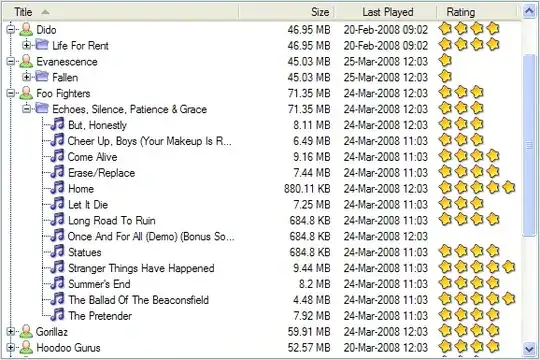

And Here

What are the proper names for both these algorithms, and is there any documentation that would allow me to better understand what's going on here? I'd google it, but I am really not sure on the specific term I should look up.

Thanks