I'm studying VHDL right now, and I have a pretty simple homework assignment - I need to build a synchronous BCD counter that will count from 0 to 9 and when it reaches 9, will go back to 0. I wanted to experiment a little so I decided not to do the code in a (at least the way I see it) traditional way (with if, elseif) but with the when-else statement (mostly due to the fact that counter is from 0 to 9 and has to go back to 0 once it hits 9).

library IEEE;

use IEEE.std_logic_1164.all;

Entity sync_counter is

port (rst, clk: in std_logic);

end Entity;

Architecture implement of sync_counter is

signal counter: integer range 0 to 10;

Begin

counter <= 0 when (rst = '1') else

counter + 1 when (clk='1' and clk'event) else

0 when (counter = 10);

end Architecture;

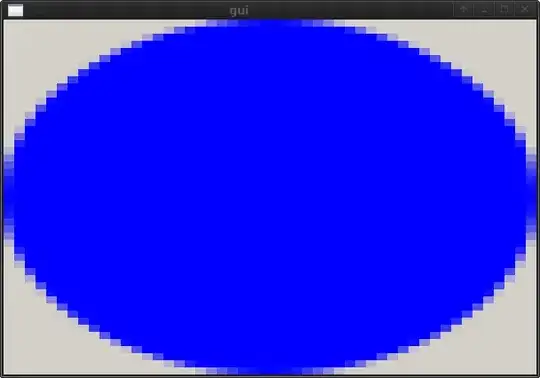

So everything compiles, but in the simulation, initially counter jumps from 0 to 2, but after a cycle (0-9 - 0) it is acting normal, meaning counter goes from 0 to 1 as it should be. Same if you force rst = '1'.

Simulation image:

Why does it jump from 0 to 2 in the start?

Thank you.