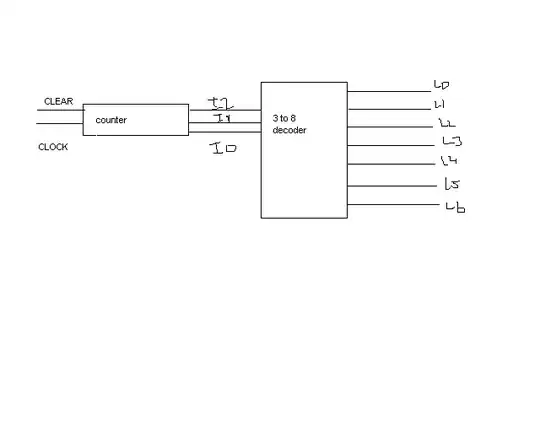

I am trying to run my 3 to 7 decoder using the inputs coming from my counter ,all the individual codes run fine but the structural code is giving up some error

This is the program for my counter

library IEEE;

use IEEE.std_logic_1164.all;

use IEEE.std_logic_unsigned.all;

entity counter is

port(clk , CLR : in std_logic;

Q : out std_logic_vector(2 downto 0) );

end counter;

architecture archi of counter is

signal tmp: std_logic_vector(2 downto 0);

begin

process (clk, CLR)

begin

if (CLR='1') then

tmp <= "000";

elsif (clk'event and clk='1') then

tmp <= tmp + 1;

end if;

end process;

Q <= tmp;

end archi;

this is the program for the decoder:

library IEEE;

use IEEE.std_logic_1164.all;

entity led_inp is

port (I : in std_logic_vector(2 downto 0) ;

L : out std_logic_vector(6 downto 0) ) ;

end led_inp ;

architecture led_inp1 of led_inp is

Begin

L(0) <= (not I(0)) and (not I(1)) and (not I(2));

L(1) <= (not I(0)) and (not I(1)) and I(2);

L(2) <= (not I(0)) and I(1) and (not I(2));

L(3) <= (not I(0)) and I(1) and I(2);

L(4) <= I(0) and (not I(1)) and (not I(2));

L(5) <= I(0) and (not I(1)) and I(2);

L(6) <= I(0) and I(1) and (not I(2));

end led_inp1;

this is the structural format for the whole design:

library IEEE;

use IEEE.std_logic_1164.all;

-- the entity of the whole design block, here i have given the names of the ports as the ones which i have used in my individual components

entity led_design is

port(clock,CLEAR :in std_logic;

L :out std_logic_vector(6 downto 0));

end led_design;

architecture led_design1 of led_design is

-- declaring my counter as a component

component counter

port(clk, CLR : in std_logic;

Q : out std_logic_vector(2 downto 0) );

end component ;

-- declaring my decoder as a component

component led_inp

port (I : in std_logic_vector(2 downto 0) ;

L : out std_logic_vector(6 downto 0)) ;

end component ;

signal I:std_logic_vector(2 downto 0);

begin

-- The PORT MAPPING BEGINS

L1: counter port map(clk=>clock,CLR=>CLEAR,I(2)=>I(2),I(1)=>I(1),I(0)=>I(0));

L2: led_inp port map(I(2)=>I(2),I(1)=>I(1),I(0)=>I(0),L(0)=>L(0),L(1)=>L(1),L(2)=>L(2),L(3)=>L(3),L(4)=>L(4),L(5)=>L(5),L(6)=>L(6));

L1: counter port

map(clk=>clock,CLR=>CLEAR,I(2)=>h(2),I(1)=>h(1),I(0)=>h(0));

end led_design1;

this is the error which comes up :ERROR

ncvhdl_p: *E,FMLBAD (led_count,85|44): poorly formed formal part of element association 87[4.3.3.2] 93[4.3.2.2].

errors: 1, warnings: 0"