I know what the inout parameters is and how to use them. Assume that we have an inout parameter io and want to create a bidirectional static RAM such as the following code :

LIBRARY ieee;

USE ieee.std_logic_1164.ALL;

ENTITY sram IS

port(

clk : IN std_logic;

wr : IN std_logic;

io : INOUT std_logic;

addr : IN INTEGER RANGE 0 TO 7

);

END sram;

ARCHITECTURE behavioral OF sram IS

TYPE matrix IS ARRAY (0 TO 7) OF std_logic;

SIGNAL mem : matrix;

BEGIN

PROCESS(clk)

BEGIN

IF rising_edge(clk) THEN

IF wr = '1' THEN

mem(addr) <= io;

END IF;

END IF;

END PROCESS;

io <= mem(addr) WHEN wr = '0' ELSE 'Z';

END behavioral;

We can create an instance of sram and write on it such as the following code :

io <= '1' WHEN wr = '1' ELSE 'Z';

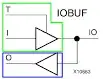

Question : How can synthesis tool control the multiple assignments and judge between multiple drivers ? What hardware is implemented to do it ?

Thanks for comments and answers ...