I want to see the power consumption of memory access in my code. My code is synthesized to a RAM128*1 in ISE (xilinx synthesis tool). I'm working on Spartan3 (3s400) and I just completed the ucf file and add a clock period in timing constrains tab.

My Code :

entity SRAM is

port(

clk : in std_logic;

wr : in std_logic;

din : in std_logic;

dout : out std_logic;

addr : in integer range 0 to 127

);

end SRAM;

architecture Behavioral of SRAM is

type matrix is array (0 to 127) of std_logic;

signal mem : matrix;

begin

process(clk)

begin

if clk = '1' and clk'event then

if wr = '1' then

mem(addr) <= din;

end if;

end if;

end process;

dout <= mem(addr);

end Behavioral;

-

Power report :

-

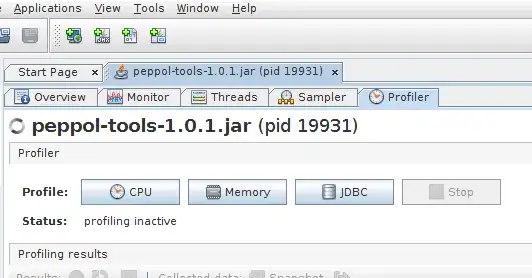

The following image is related to the Logic power consumption with details provided by Xilinx XPower Analyzer :

My question is why the (Logic) power is zero ? How can I see the power related to memory access that depends on size of memory?