As far as I know, there are 4 types of FSM. Mealy, Moore, Medvedev, and registered output. In registered output, you can have up to 4 processes (you can find an example here). In Medvedev, there can be 1 or 2. In others, there can be 1 or 2 processes for the state-machine, and 1 process for output that can be merged with the combinational process.

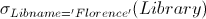

Suppose this FSM:

One-Process FSM VHDL code for that would be:

FSM_FF: process (CLK, RESET)

begin

if RESET='1' then

STATE <= START;

elsif CLK'event and CLK='1' then

case STATE is

when START =>

if X=GO_MID then

STATE <= MIDDLE;

end if;

when MIDDLE =>

if X=GO_STOP then

STATE <= STOP;

end if;

when STOP =>

if X=GO_START then

STATE <= START;

end if;

when others => STATE <= START;

end case;

end if;

end process FSM_FF;

Two-Process FSM VHDL code:

FSM_LOGIC: process( STATE, X)

begin

case STATE is

when START =>

if X=GO_MID then

NEXT_STATE <= MIDDLE;

end if ;

when MIDDLE =>

...

when others => NEXT_STATE <= START;

end case;

end process FSM_LOGIC;

---------------------------------------------

FSM_FF: process(CLK, RESET)

begin

if RESET='1' then

STATE <= START;

elsif CLK'event and CLK='1' then

STATE <= NEXT_STATE;

end if;

end process FSM_FF;

WHICH ONE SHOULD YOU USE?

According to Jensen,

It depends on a number of things. Do you need a Moore machine or a

Mealy machine? Is the downstream logic that received the output signal

synchronous or combinatorial? It also depends on which style of coding

you prefer.

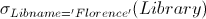

Prof. Saheb Zamani compared the 1-Process and 2-Process from three aspects (slide 86):

- Structure and Readability: From the hardware perspective, combinational and sequential elements are two different things, so a

separated design is closer to hardware. On the other side, the

graphical FSM (without output equations)

resembles more a 1 process than a 2 process description.

- Simulation: Error detection easier with two state processes due to access to

intermediate signals.

- Synthesis: 2 state processes can lead to smaller generic netlist and therefore

to better synthesis results (depends on synthesizer but in general,

it is closer to hardware)

P.S. I couldn't find the original sources for these links, so I just added the sources that I used. But this one is more comprehensive and includes some examples as well.