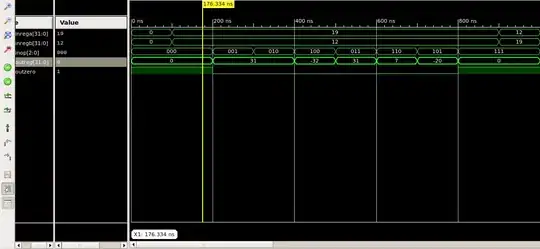

I wrote this VHDL-program vor an ALU and its testbench that is working:

ALU-code:

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

use IEEE.NUMERIC_STD.ALL;

entity ALU_CLK is

port( Clk : in std_logic; --clock signal

InRegA,InRegB : in signed(31 downto 0); --input operands

InOp : in unsigned(2 downto 0); --Operation to be performed

OutReg : out signed(31 downto 0); --output of ALU

OutZero : out std_logic

);

end ALU_CLK;

architecture Behavioral of ALU_CLK is

signal Reg1,Reg2,Reg3 : signed(31 downto 0) := (others => '0');

begin

Reg1 <= INregA;

Reg2 <= InRegB;

OutReg <= Reg3;

process(Clk)

variable temp: signed(31 downto 0);

begin

if(rising_edge(Clk)) then

case InOp is

when "010" =>

temp := Reg1 + Reg2; --addition

when "000" =>

temp := Reg1 and Reg2; --AND gate

when "001" =>

temp := Reg1 or Reg2; --OR gate

when others =>

NULL;

end case;

if temp = (31 downto 0=>'0') then

OutZero <= '1';

else

OutZero <= '0';

end if;

Reg3 <= temp;

end if;

end process;

end Behavioral;

The testbench code:

LIBRARY ieee;

USE ieee.std_logic_1164.ALL;

USE ieee.numeric_std.ALL;

ENTITY tb IS

END tb;

ARCHITECTURE ALU_CLK OF tb IS

signal Clk : std_logic := '0';

signal A,B,R : signed(31 downto 0) := (others => '0');

signal Op : unsigned(2 downto 0) := (others => '0');

signal zero : std_logic :='0';

constant Clk_period : time := 10 ns;

BEGIN

uut: entity work.ALU_CLK PORT MAP (

Clk => Clk,

InRegA => A,

InRegB => B,

InOp => Op,

OutReg => R,

OutZero => zero

);

Clk_process :process

begin

Clk <= '0';

wait for Clk_period/2;

Clk <= '1';

wait for Clk_period/2;

end process;

-- Stimulus process

stim_proc: process

begin

wait for Clk_period*1;

--test normal operations

A <= "00000000000000000000000000010011"; --19 in decimal

B <= "00000000000000000000000000001100"; --12 in decimal

Op <= "000"; wait for Clk_period; --Bitwise and A and B

Op <= "001"; wait for Clk_period; --Bitwise or B from A.

Op <= "010"; wait for Clk_period; --addition A nad B

wait;

end process;

END;

To shorten the code listings a bit I did not post all the operations the ALU does. I can manage it to change the ALU to one without the clk but how can I test it with a testbench?