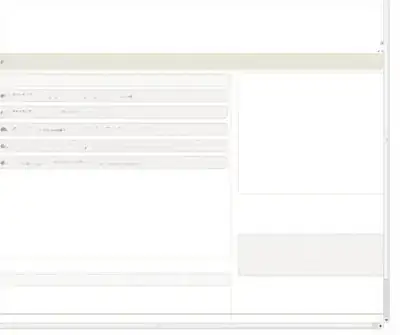

I am working on generating a 40 bit length pulse train. I also must be able to adjust the frequency. I tried to make a new low frequency clock and i make a new counter which counts on it's rising edges and give an high output and terminating after 40 bit. It's not working. I tried some other methods. They are not, too.

For example;

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

use IEEE.NUMERIC_STD.all;

entity con40 is port(clk:in std_ulogic; q:out std_ulogic);

end entity con40;

architecture Behaviour of con40 is

constant s:std_ulogic_vector:="11111111111111111111111111111111";

signal i:unsigned(4 downto 0):="00000";

signal en:std_logic:='1';

signal reset:std_logic:='0';

begin

q<=s(to_integer(i));

process(reset,clk) is begin

if reset='1' then

i<=(others=>'0');

elsif rising_edge(clk) then

if en='1' then

i<=i+1;

end if;

end if;

end process;

end architecture Behaviour;

There is 32-bit length in this code but i wanna make 40 bit but whatever, this is not working too. I think methods for such a pulse train must be common and they are being used widely. But hey! unluckily i can find nothing useful.