i need a frequency divider in verilog, and i made the code below. It works, but i want to know if is the best solution, thanks!

module frquency_divider_by2 ( clk ,clk3 );

output clk3 ;

reg clk2, clk3 ;

input clk ;

wire clk ;

initial clk2 = 0;

initial clk3 = 0;

always @ (posedge (clk)) begin

clk2 <= ~clk2;

end

always @ (posedge (clk2)) begin

clk3 <= ~clk3;

end

endmodule

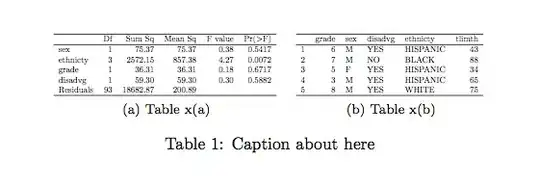

the circuit generated by quartus: