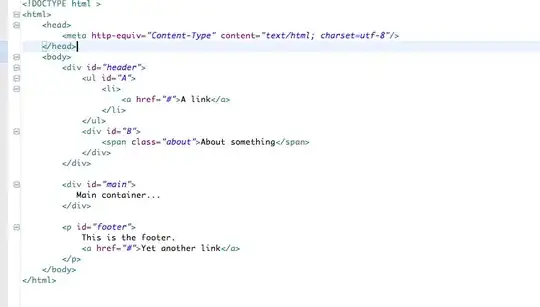

I've written code for a binary divider that takes in an 8 bit dividend, 3 bit divisor, and gives a 5 bit quotient (3 bit remainder). I've literally spent hours trying to fix a bug that gives incorrect results but I haven't been able to identify it. Any help would be GREATLY appreciated! I basically get wrong answers for my inputs but I can't figure out why. There is a bus that takes in values and on the first clock cycle where st is 1, the dividend register is loaded. On the second clock cycle after, the divisor register is loaded and the calculation is made for the next three clock cycles.

The V signal is the output to signify that an overflow has occured (the result can't be fit into the five bits of the quotient), my st is the start signal to start the process, sh is the shift signal for the shift register, su is the subtract signal for the subtractor.

library IEEE;

use IEEE.STD_LOGIC_1164.all;

use IEEE.STD_LOGIC_ARITH.all;

use IEEE.STD_LOGIC_UNSIGNED.all;

entity Divider is

Port (bus_in: in std_logic_vector(8 downto 0);

St, Clk, reset: in std_logic;

Quotient: out std_logic_vector(4 downto 0);

Remainder: out std_logic_vector(2 downto 0);

v: out std_logic);

end Divider;

architecture Behavioral of Divider is

signal State, NextState: integer range 0 to 5;

signal C, Ld1, Ld2, Su, Sh: std_logic;

signal Divisor: std_logic_vector(2 downto 0);

signal Subout: std_logic_vector(3 downto 0);

signal Dividend: std_logic_vector(8 downto 0);

begin

Subout <= Dividend(8 downto 5) - ('0' & divisor);

C <= not Subout (3);

Remainder <= Dividend(7 downto 5);

Quotient <= Dividend(4 downto 0);

State_Graph: process (State, St, C)

begin

Ld1 <= '0';

Ld2<='0';

v <= '0';

Sh <= '0';

Su <= '0';

case State is

when 0 =>

if (St = '1') then

Ld1 <= '1';

NextState <= 1;

else

NextState <= 0;

end if;

when 1 =>

if (St = '1') then

Ld2 <= '1';

NextState <= 2;

else

Ld2<='1';

NextState <= 2;

end if;

when 2 =>

if (C = '1') then

v <= '1';

NextState <= 0;

else

Sh <= '1';

NextState <= 3;

end if;

when 3 | 4 =>

if (C = '1') then

Su <= '1';

NextState <= State;

else

Sh <= '1';

NextState <= State + 1;

end if;

when 5 =>

if (C = '1') then

Su <= '1';

end if;

NextState <= 0;

end case;

end process State_Graph;

Update: process (Clk)

begin

if Clk'event and Clk = '1' then

State <= NextState;

--if Load = '1' then

-- Dividend <= '0' & bus_in;

--end if;

if Ld1 = '1' then

Dividend <= '0'&Bus_in(7 downto 0);

end if;

if Ld2 = '1' then

Divisor <= Bus_in(2 downto 0);

end if;

if Su = '1' then

Dividend(8 downto 5) <= Subout;

Dividend(0) <= '1';

end if;

if Sh = '1' then --94

Dividend <= Dividend(7 downto 0) & '0';

end if;

end if;

end process update;

end Behavioral;

Here's my input and outputs:

[Signals]: https://i.stack.imgur.com/s1w1l.jpg 1

The picture shows that my registers for the divisor and dividend is loading correctly. So I think the issue is with the actual division code. The state machine also seems to be working correctly.