module binarytogray #(

parameter PTR=2

)(

input logic [PTR:0] binary_value,

output logic [PTR:0] gray_value

);

genvar i;

generate

for(i=0;i<PTR;i=i+1) begin:for_loop

assign gray_value[i]=binary_value[i]^binary_value[i+1];

end

endgenerate

assign gray_value[PTR]=binary_value[PTR];

endmodule

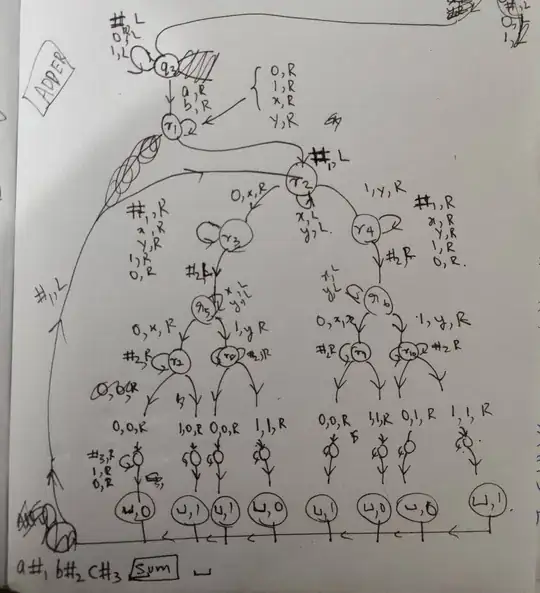

This binary to gray conversion code is an example from a book. Can anybody explain:

assign gray_value[i]=binary_value[i]^binary_value[i+1];

I am not able to understand this specific XOR operation for converting to gray code from binary.

Example on EDAplayground.