Ive made a simple ticker module that produces a rick every time the counter reaches 163. Here is the code for it:

module baud_gen(

input clock,

input reset,

output tick

);

reg [7:0] count;

always @ (posedge clock)

begin

if(reset || (count == 163))

count <= 0;

else

count <= count + 1;

end

assign tick = (count == 163) ? 1:0;

endmodule

It works as it should, in simulation when the counter reaches 163, tick is assigned high and otherwise its 0.

Now I instantiated this into my UART receiver. Here is the code snippet:

module receiver(

input clock,

input reset,

input s_tick,

input rx,

output reg done,

output [7:0] word_out

);

localparam [1:0]

idle = 00,

start = 01,

data = 10,

stop = 11;

baud_gen ticker (.clock(clock), .reset(reset), .tick(s_tick));

.

.

.

.

Now when I run the simulation for the receiver module. The ticker does not work correctly. Here instead of producing a 1 at count==163 it produces a x.

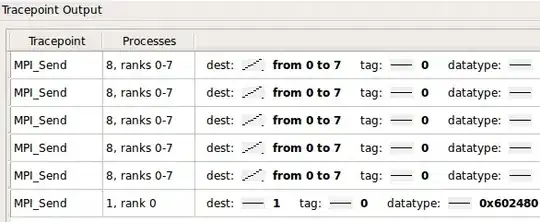

Here is the simulation of it when it has been instantiated into receiver module:

I cannot figure out why this change in behavior. Thank you for looking