MY PROBLEM

I have a SIMULINK model that has got a feeback loop aka Algebraic Loops that is causing error in the simulation. My original solver configuration was Fixed-Step with Dormand-Prince (Order 5). I also tried Fixed-Step with Order 3 (Runga-Kutta). It still has not resolved the issue.

MY QUESTION

Is there any way to resolve algebraic loop without altering the original performance or design of the circuit too much?

CLARIFICATION FOR THE QUESTION

I am sure that there will be a way to solve this. However, I don't want it to compromise the original performance of the circuit. Moreover, it is a customer-supplied data and it seems that they have managed to work this out as fine. I simply require somebody to point me to the right direction regarding how to solve this.

MY Approach so far

I tried to break the loop using:

i) Switch (if ip = 0, op = 0; if ip = 1, op = 1) I know it is stupid but it is a different block that breaks the loop.

ii) Logic gate (XORing the feedback signal with 0).

Unfortunately, I don't know how to do a zero-order hold unit delay loop that seems to be another commonly prescribed solution for this kind of problem. But I believe that may cause issues with my model's originally intended performance.

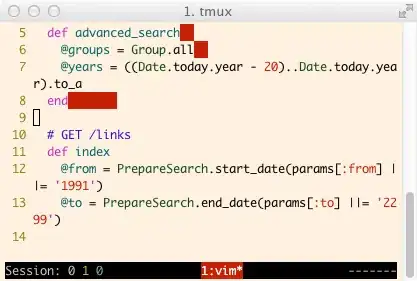

I have posted a query on Mathworks website, but no response so far. SO I thought...why not stackoverflow? Below is the image.