I'm coding a simple shift register using if else block. I noticed that the else block works as it should when the control signal is control = 2'b00 (meaning it retains the default vale) but when I give the control value control = 2'b11 it starts shifting to the right, which is not what I want.

Why does the else block work selectively? Even when both control = 2'b00 and control = 2'b11 fall in the else case?

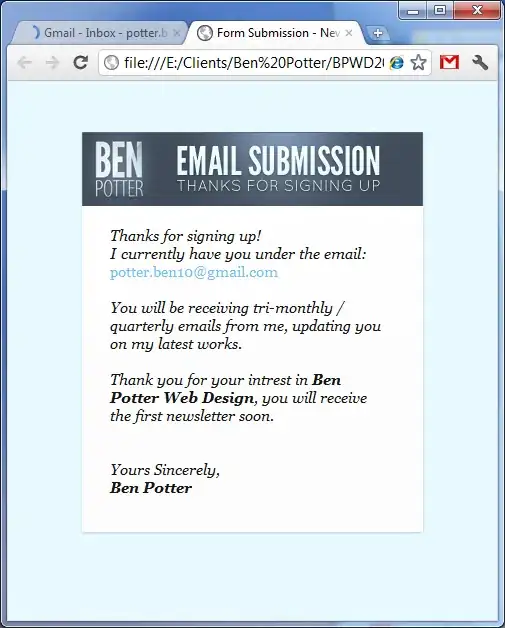

Code and screenshot below:

module shift(

input clock,

input reset,

input [1:0] control,

input in,

output [7:0] out

);

reg [7:0] r_reg, r_next; //a 7 bit shift register which will be output as is, this can be changed to any size

always @ (posedge clock or posedge reset)

begin

if(reset)

r_reg <= 0;

else

r_reg <= r_next;

end

always @ (*)

begin

if(control[0]) //shift right

r_next = {in, r_reg[7:1]};

else if(control[1]) //shift left

r_next = {r_reg[6:0], in};

else

r_next = r_reg; //default state stays the same

end

assign out = r_reg;

endmodule

EDIT:

if(right) //shift right

r_next = {in, r_reg[7:1]};

else if(left) //shift left

r_next = {r_reg[6:0], in};

else if((~right & ~left) || (right & left))

r_next = r_reg; //default state stays the same

The above did not work either.. But I fixed it with case.

case(control)

2'b01: r_next = {in, r_reg[7:1]};

2'b10: r_next = {r_reg[6:0], in};

default: r_next = r_reg;