I am currently working on a project in Verilog HDL with an FPGA obtained from my school (I am running Quartus II vers. 10.1 and 11.0 (I've tried both)). I am getting a very bizarre bug that I cannot figure out for the life of me.

I am developing a Morse Code program which detects dots and dashes, and then outputs the appropriate letter on a HEX display based upon this input. The HEX display works beautifully, but my UserInput module doesn't seem to do anything at all!

module UserInput(Clock, reset, in, out);

input Clock, reset, in;

output reg [1:0] out;

wire [2:0] PS;

reg [2:0] NS;

parameter NONE = 2'b00, DOT = 2'b01, DASH = 2'b11; //For Output

parameter UP = 3'b000, SHORT0 = 3'b001, SHORT1 = 3'b010, UP_DOT = 3'b011, LONG = 3'b100, UP_DASH = 3'b101;

//Active High

always@(PS or in)

case (PS)

UP: if (in) NS = SHORT0;

else NS = UP;

SHORT0: if (in) NS = SHORT1;

else NS = UP_DOT;

SHORT1: if (in) NS = LONG;

else NS = UP_DOT;

UP_DOT: NS = UP;

LONG: if (in) NS = LONG;

else NS = UP_DASH;

UP_DASH: NS = UP;

default: NS = 3'bxxx;

endcase

always@(PS)

case (PS)

UP: out = NONE;

SHORT0: out = NONE;

SHORT1: out = NONE;

UP_DOT: out = DOT;

LONG: out = NONE;

UP_DASH: out = DASH;

default: out = 2'bxx;

endcase

D_FF dff0 (PS[0], NS[0], reset, Clock);

D_FF dff1 (PS[1], NS[1], reset, Clock);

D_FF dff2 (PS[2], NS[2], reset, Clock);

endmodule

module D_FF (q, d, reset, clk);

input d, reset, clk;

output reg q;

always@(posedge clk or posedge reset)

begin

if (reset) q = 0;

else q = d;

end

endmodule

The input for the module is a KEY on the FPGA. The FSM represented by the UserInput module has the key be in the "UP" state at t=0. Then, if there is input, it will move through SHORT0 or SHORT1, and finally LONG. If it the key is released at any of these states, they go to their appropriate intermediary UP states and provide an output of "DOT" or "DASH".

However, when I connect this to my FPGA, I get nothing. From my testing, it seems that it never moves away from the "UP" state. Even my simulations give me nothing. Secondly, I've tried connecting a different UserInput module from a different project (one I know works), and still nothing. Is there something going on in the background of Verilog I am missing?

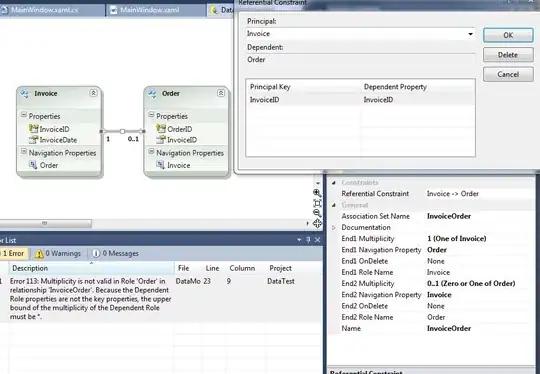

Here is an image of the simulation waveform:

DFf 0, 1, and 2 are the bits 0, 1, and 2 of PS. My simulation won't allow a showing of the NS.