I have made some verilog code and a test bench to create a T flip flop but cannot get the outputs to change to anything other than x. I've tried doing o/p as reg in the module and the testbench and then assigning the tb reg to a wire but didn't work. Not sure where it's being hung up.

Below is the flip flop module:

module Tflipflop(input T, S, R, En, clk, output reg Q, output Qn);

assign Qn = ~Q;

always@(posedge clk | R | S) begin

if(R == 1'b1)

Q <= 1'b0;

else if (S ==1'b1)

Q <= 1'b1;

else if (En==1'b1) begin

case(T)

1'b1: Q <= ~Q;

1'b0: Q <= Q;

default: Q <= Q;

endcase

end

else

Q <= Q;

end

endmodule

Below is the testbench:

`timescale 1ns/1ps

module Tflipflop_tb();

reg T, S, R, En, clk;

wire Qn, Q;

Tflipflop TFF_1(.T(T), .S(S), .R(R), .En(En), .clk(clk), .Q(Q), .Qn(Qn));

initial begin

clk = 0; T = 1; S = 0; R = 0; En = 1; #5;

clk = 1; #5;

clk = 0; #5;

clk = 1; #5;

clk = 0; #5;

clk = 0; #5;

clk = 1; #5;

clk = 0; En = 0; #5;

clk = 1; #5;

clk = 0; #5;

clk = 1; #5;

end

endmodule

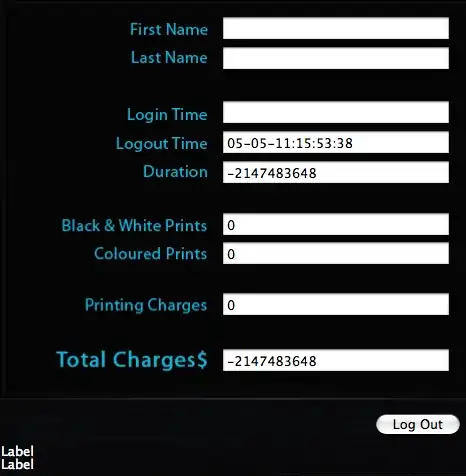

a picture of the simulation in modelsim: