I'm doing a research about how memory is managed in RTEMS using an ARM-based Xilinx Zynq. The program runs on two cores with SMP.

I have read about memory barriers and out-of-order execution paradigm, I concluded that a barrier or a fence is a hardware implementation rather than software.

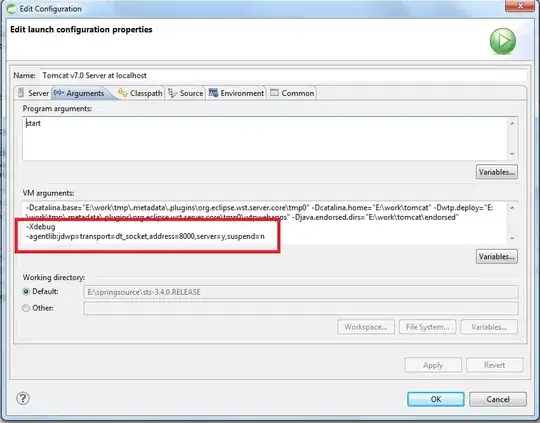

RAM is divided in several sections, however there are some sections called barriers which shared areas with other sections. I attach you a capture.

xbarrier starts where the next section begins and ends where previous section ends. Another example:

In this one, the barrier starts at the same addres as the previous section and it ends before the next section starts.

Are these memory sections related with barrier instructions? Why are these memory sections implemented?

Thanks in advance,