Nice question, and your instructor is right - this circuit will oscillate if both S and R are released at the "same" time. Your issue is that your TB isn't doing this, but this one does:

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

entity TOP is

end entity TOP;

architecture A of TOP is

signal S,R,Q,NOTQ: std_logic;

component SRLATCH_VHDL is

port(

S : in std_logic;

R : in std_logic;

Q : inout std_logic;

NOTQ : inout std_logic);

end component SRLATCH_VHDL;

begin

U1 : SRLATCH_VHDL port map(S, R, Q, NOTQ);

process is

begin

S <= '1';

R <= '1';

wait for 10 ns;

S <= '0';

R <= '0';

wait;

end process;

end architecture A;

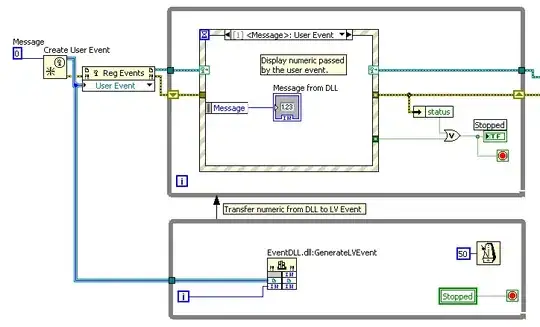

This will produce infinite delta-delay oscillation:

This isn't a great way to demonstrate asynchronous behaviour, because you are effectively simplifying the physical nature of the circuit, and using the VHDL scheduler to show that there's a problem (with the use of 'delta delays'). A better way to do this is to model real circuit behaviour by adding signal delays (this is exactly what your tools are doing when they back-annotate for timing simulations). Look up signal assignments with after, and the difference between transport and inertial delays. If you draw a circuit diagram, you'll see that the issue arises if both S and R are released in a 'small' time window that doesn't allow the signal propagation around your circuit to complete before the second control signal changes. You now need to write a testbench that changes S and R inside this time window.

Pretty much everything you ever design will be asynchronous, in exactly the same way as your SR circuit. We make circuits 'synchronous' only by ensuring that input signals don't change at the same time. The job of the timing tools is to tell us what 'same' actually means: when you get a report or a datasheet value giving you a setup or a hold time, then that number is simply the numerical version of 'not the same'.